TMS320C6657CZHA IC DSP FIX/FLOAT POINT 625FCBGA

Laina Huahana

wehewehe

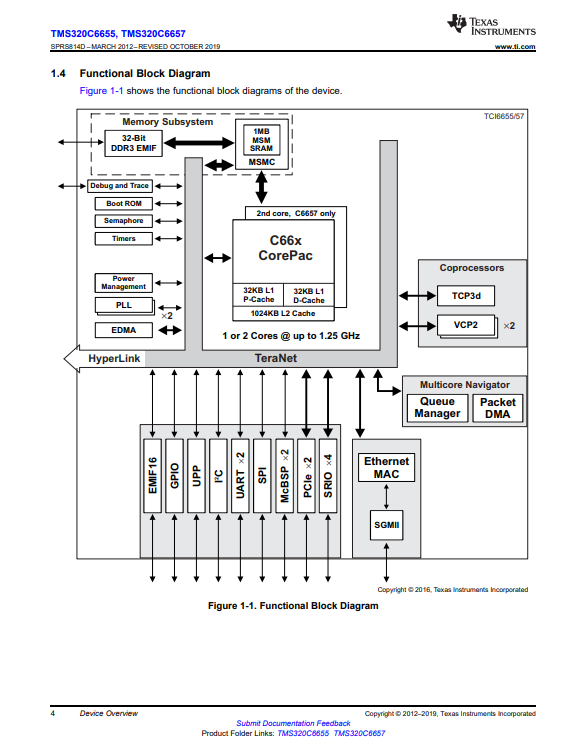

Hāʻawi ka TI's KeyStone architecture i kahi papahana papahana e hoʻohui ana i nā subsystem like ʻole (C66x cores, memory subsystem, peripherals, and accelerators) a hoʻohana i kekahi mau mea hou a me nā ʻenehana e hoʻonui ai i ke kamaʻilio intradevice a me ka interdevice e hiki ai i nā kumuwaiwai DSP ke hana maikaʻi a maʻalahi.ʻO ke kikowaena o kēia hoʻolālā nā mea nui e like me Multicore Navigator e hiki ai ke hoʻokele pono i ka ʻikepili ma waena o nā ʻāpana like ʻole.ʻO ka TeraNet kahi lole hoʻololi nonblocking e hiki ai i ka neʻe ʻana o ka ʻikepili kūloko wikiwiki a me ka paio ʻole.Hiki i ka multicore shared memory controller ke komo i ka hoʻomanaʻo kaʻana like a me waho me ka ʻole o ke kaha kiʻi ʻana mai ka mana lole lole.No ka hoʻohana ʻana i ka helu paʻa, ʻo ka C66x core he 4 × ka mana hoʻonui (MAC) o nā cores C64x+.Eia kekahi, hoʻohui ka C66x core i ka hiki i ka floating-point a me ka hoʻokō helu helu per-core he 40 GMACS alakaʻi i ka ʻoihana a me 20 GFLOPS i kēlā me kēia kumu (@1.25 GHz hana pinepine).Hiki i ka C66x core ke hoʻokō i nā hana MAC floating-point hoʻokahi pololei i kēlā me kēia pōʻai a hiki ke hana i nā hana pālua a hui pū ʻia a hoʻokō ʻo IEEE 754.Hoʻokomo ka C66x core i 90 mau ʻōlelo aʻo hou (i hoʻohālikelike ʻia me ka C64x+ core) i manaʻo ʻia no ka hoʻoili ʻana i ka helu lana a me ka vector math.Hāʻawi kēia mau mea hoʻonui i ka hoʻomaikaʻi ʻana i ka hana nui i nā kernel DSP kaulana i hoʻohana ʻia i ka hana hōʻailona, ka makemakika, a me nā hana kiʻi kiʻi.ʻO ka C66x core ka code-compatible me ka C6000 o ka hanauna mua o ka C6000 paʻa-a me ka floating-point DSP cores, e hōʻoiaʻiʻo ana i ka lawe ʻana i nā polokalamu a me nā pōʻai hoʻomohala polokalamu pōkole no nā noi e neʻe ana i ka mīkini wikiwiki.Hoʻohui ka C665x DSP i ka nui o ka hoʻomanaʻo ma-chip.Ma kahi o 32KB o ka papahana L1 a me ka waihona ʻikepili, hiki ke hoʻonohonoho ʻia ʻo 1024KB o ka hoʻomanaʻo i hoʻolaʻa ʻia e like me RAM palapala ʻia a i ʻole cache.Hoʻohui pū ka hāmeʻa i ka 1024KB o Multicore Shared Memory hiki ke hoʻohana ʻia ma ke ʻano he L2 SRAM kaʻana a/a i ʻole ka L3 SRAM.Hoʻopili nā mea hoʻomanaʻo L2 āpau i ka ʻike hewa a me ka hoʻoponopono hewa.No ke komo wikiwiki ʻana i ka hoʻomanaʻo waho, loaʻa i kēia hāmeʻa kahi 32-bit DDR-3 external memory interface (EMIF) e holo ana ma ka wikiwiki o 1333 MHz a loaʻa iā ECC DRAM kākoʻo.

| Nā kikoʻī: | |

| ʻAno | Waiwai |

| Māhele | Nā Kaapuni Hoʻohui (IC) |

| Hoʻokomo ʻia - DSP (Nā Mea Hana Hōʻailona Kikohoʻe) | |

| ʻO Mfr | Nā mea kani ʻo Texas |

| moʻo | TMS320C66x |

| Pūʻolo | pā |

| Kūlana Māhele | ʻeleu |

| ʻAno | Lae Pa'a/Lana |

| Ikepili | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Uku Uku | 1GHz |

| Hoʻomanaʻo Volatile ʻole | ROM (128kB) |

| Ma-Chip RAM | 2.06MB |

| Voltage - I/O | 1.0V, 1.5V, 1.8V |

| Voltage - Core | 1.00V |

| Ka Mahana Hana | -40°C ~ 100°C (TC) |

| ʻAno kau ʻana | Mauna ʻili |

| Pūʻolo / hihia | 625-BFBGA, FCBGA |

| Pūʻolo Mea Mea Hoʻolako | 625-FCBGA (21x21) |

| Helu Huahana Kumu | TMS320 |

PiliHANA

-

Tel

-

leka uila

-

skype

-

whatsapp

whatsapp